DDS(ダイレクト・デジタル・シンセサイザ)回路の受託設計。

(有)安田電子設計事務所では、FPGAを使用したDDS(ダイレクト・デジタル・シンセサイザ)設計サービスを承っております。

各種請け負いますので、ご依頼内容はお問い合わせください。

任意の周波数を得るのに昔はPLLシンセサイザが用いられていましたが、今ではより広範囲に高分解能な設定が可能なDDSが主流です。

DDS はダイレクト・デジタル・シンセサイザの略で、デジタル信号処理によって任意の周波数と任意の波形が出力できる方式です。

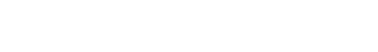

図1は通常のDDSの動作原理を説明するブロック図です。

DDSは専用ICとして数多くの種類が市販されており、例えば Analog Devices のAD9833等があります。AD9833は 28ビットのアキュムレータと28ビットの周波数設定レジスターを持っています。

周波数設定レジスターに 1を設定すると、クロック毎にアキュムレータの値は+1され 228回のクロックで 1周します。 228の 1/2 を設定すると 2回のクロックで 1周します。このようにしてアキュムレータから周波数設定レジスターに設定した値に応じた周波数出力を得ることができます。

またROMによってアキュムレータの出力を正弦波などに変換するROMと、それをアナログ値に変換するDACを持っています。ROMの内容によって正弦波や三角波、方形波などのアナログ波形を得ることができます。

クロックに25MHzを使用すると 0~12.5MHzを出力することができ、分解能は25,000,000/228 = 0.0931Hz となります。

このように高分解能ですが、周波数はレジスター設定値×0.093 となり半端な値になります。また0.093も約であり正確には 0.093132257... と割り切れません。

分解能を0.1Hzときっちりしようとすると、クロックは228 ×0.1Hz = 26,843,545.6Hzとなり、半端な値でカスタムで作らない限りちょっと入手困難です。

ところが、安田電子設計事務所ではオリジナルのDDS方式を発明し(特許出願中)、例えば 20MHz といった周波数の水晶発振子を用いてもきっちり1Hz単位の設定ができ、また小数点以下何桁でも水晶精度の正確な周波数を設定でき、例えば 9999.9999Hz でも水晶精度を損ねることなく簡単に設定できるDDSを提供できます。

FPGAを用いたDDS回路設計の事例を紹介します。

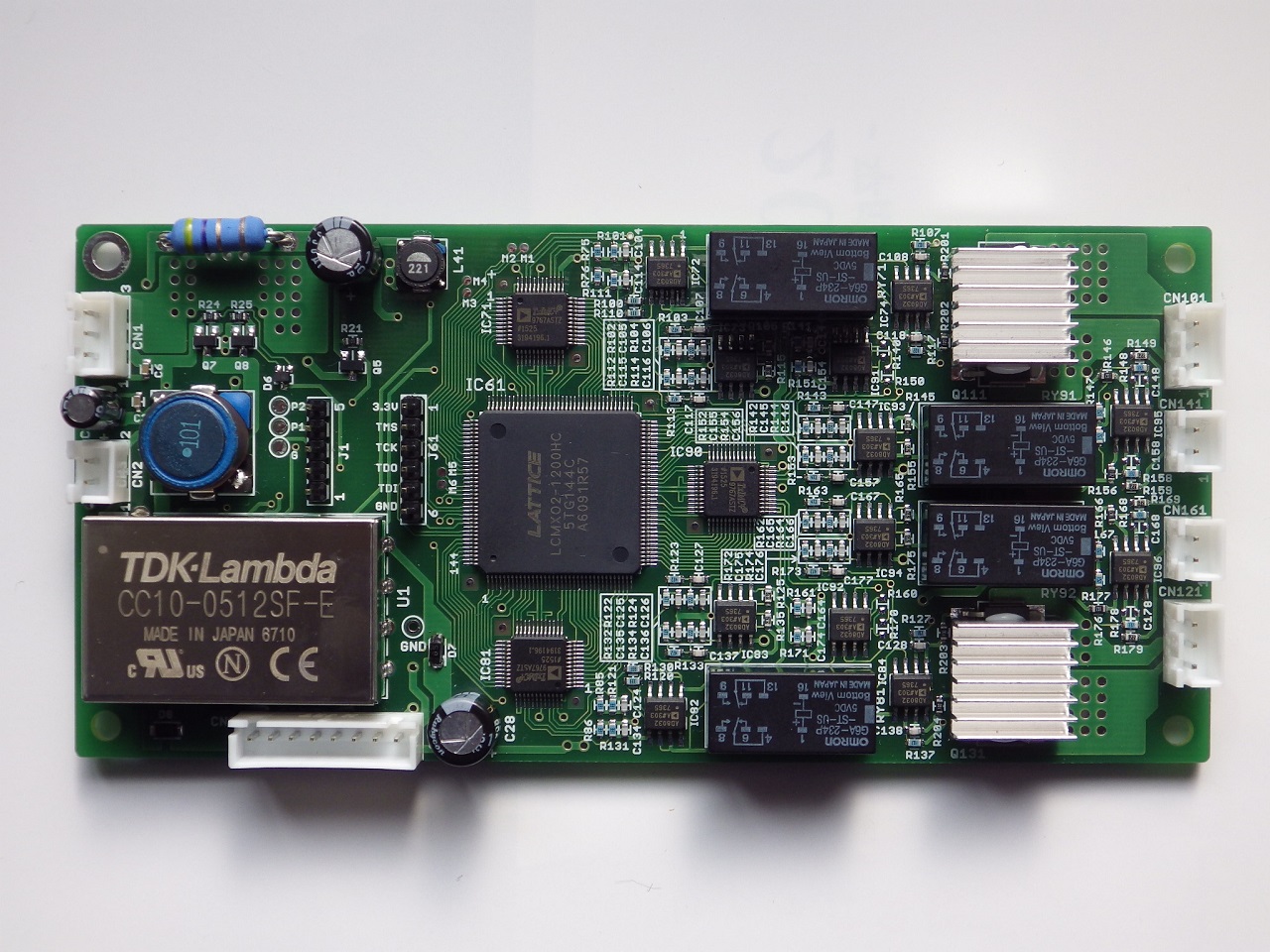

写真1は安田電子設計事務所で試作した非常に高精度な3チャンネルの DDS の事例です。

通常はDDSは専用ICを購入しますが、ちょっと特殊なものになると売られていません。そこでFPGAを使用してDDSを設計しました。

それによって正弦波、矩形波、鋸歯状波などを同時に出力可能です。

クロックには温度補償水晶発振器を使用し、±2ppm の絶対精度を得ています。

安田電子設計事務所はFPGAで高精度なDDSを設計する独自の技術を保有しています。